## MSP430 | Clock do sistema

Luiz Fernando Pinto de Oliveira

20 de julho de 2018

/ 15

#### Clock - Funcionalidades

#### Características:

- Possui duas, três ou quatro fontes de clock:

- LFXT1CLK: Oscilador de baixa frequência / alta frequência que pode ser usado com cristais de relógio de baixa frequência ou fontes de relógio externas de 32768 Hz ou com cristais padrão, ressonadores ou fontes de relógio externas na faixa de 400-kHz a 16-MHz;

- XTŽCLK: Oscilador de alta frequência opcional que pode ser usado com cristais padrão, ressonadores ou fontes de relógio externas na faixa de 400 kHz a 16 MHz;

- DCOCLK: Oscilador interno controlado digitalmente(DCO);

- VLOCLK: Oscilador interno de baixa potência e baixa frequência com frequência típica de 12 kHz.

- Três sinais de relógio estão disponíveis no módulo básico de *clock*, são elas:

- ACLK: Clock auxiliar. O ACLK é selecionável por software como LFXT1CLK ou VLOCLK. O ACLK é dividido por 1, 2, 4 ou 8. O ACLK é selecionável por software para módulos periféricos individuais;

- MCLK: Clock mestre. O MCLK é selecionável por software como LFXT1CLK, VLOCLK, XT2CLK (se disponível no chip) ou DCOCLK. O MCLK é dividido por 1, 2, 4 ou 8. O MCLK é usado pela CPU e pelo sistema;

- SMCLK: Clock sub-principal. O SMCLK é selecionável por software como LFXT1CLK, VLOCLK, XT2CLK (se disponível no chip) ou DCOCLK. O SMCLK é dividido por 1, 2, 4 ou 8. O SMCLK é selecionável por software para módulos periféricos individuais.

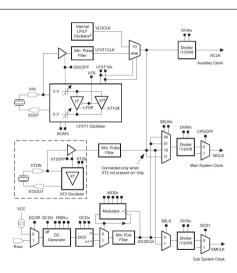

#### Clock - Diagrama de blocos do sistema de clock

#### Clock - Operação

- O sistema de *clock* do MSP430 pode ser configurado ou reconfigurado por *software* a qualquer momento durante a execução do programa;

- Os registradores de configuração do clock do sistema são: DCOCTL, BCSCTL1, BCSCTL2 e BCSCTL3.

#### Clock - DCOCTL, Registrador de controle do DCO

| DCOCTL    |                 |  |  |  |  |  |  |  |

|-----------|-----------------|--|--|--|--|--|--|--|

| 7         | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

| DCOx MODx |                 |  |  |  |  |  |  |  |

- DCOx: Seleção de frequência de DCO. Esses bits selecionam qual das oito frequências DCO distintas dentro do intervalo definido pela configuração RSELx é selecionada;

- MODx: Seleção de modulador. Esses bits definem com que frequência a frequência  $f_{DCO+1}$  é usada dentro de um período de 32 ciclos DCOCLK. Durante os demais ciclos de clock (32-MOD), a frequência  $f_{DCO}$  é usada. Não utilizável quando DCOx = 7.

## Clock - BCSCTL1, Reg. de controle do clock do sistema 1 !

| BCSCTL1 |                        |  |  |  |  |  |  |  |

|---------|------------------------|--|--|--|--|--|--|--|

| 7       | 7 6 5 4 3 2 1 0        |  |  |  |  |  |  |  |

| XT2OFF  | XT2OFF XTS DIVAx RSELx |  |  |  |  |  |  |  |

- **XT20FF**: XT2 desligado. Este bit desliga o oscilador XT2:

- 0 XT2 está ativado:

- 1 XT2 está desativado se não for usado para MCLK ou SMCLK.

- XTS: Seleção do modo LFXT1:

- 0 modo de baixa freguência:

- 1 modo de alta freguência.

- **DIVA**x: Divisor para ACLK:

- **▶** 00 /1;

- **▶** 01 /2:

- **▶** 10 /4;

- **▶** 11 /8.

- RSELx: Faixa de seleção. Dezesseis faixas de frequência diferentes estão disponíveis. A faixa de frequência mais baixa é selecionada configurando RSELx = 0. RSEL3 é ignorado quando DCOR = 1.

# Clock - BCSCTL2, Reg. de controle do clock do sistema 2

6 / 15

| BCSCTL2     |                 |  |      |       |  |      |  |  |

|-------------|-----------------|--|------|-------|--|------|--|--|

| 7           | 7 6 5 4 3 2 1 0 |  |      |       |  |      |  |  |

| SELMx DIVMx |                 |  | SELS | DIVSx |  | DCOR |  |  |

- SELMx: Selecione MCLK. Esses bits selecionam a fonte MCLK:

- 00 DCOCLK;

- ► 01 DCOCLK:

- 10 XT2CLK quando o oscilador XT2 apresenta no chip. LFXT1CLK ou VLOCLK quando o oscilador XT2 não está presente no chip;

- ▶ 11 LFXT1CLK ou VLOCLK.

- **DIVMx**: Divisor para MCLK:

- 00 /1;

- 01 /2

- 10 /4:

- ► 11 /8.

- SELS: Selecione SMCLK. Este bit seleciona a origem do SMCLK:

- 0 DCOCLK;

- ▶ 1 XT2CLK quando o oscilador XT2 está presente. LFXT1CLK ou VLOCLK quando o oscilador XT2 não está presente.

- DIVSx: Divisor para SMCLK:

- **00** /1:

- **0**1 /2;

- **1**0 /4:

- ► 11 /8.

- DCOR: Seleção do resistor DCO. Não disponível em todos os dispositivos. Veja a folha de dados específica do dispositivo:

- 0 para resistor interno:

- 1 para resistor externo.

#### Clock - BCSCTL3, Reg. de controle do clock do sistema 3

| BCSCTL3 |                 |      |      |     |             |       |         |  |  |

|---------|-----------------|------|------|-----|-------------|-------|---------|--|--|

| 7       | 7 6 5 4 3 2 1 0 |      |      |     |             |       |         |  |  |

| XT2Sx   |                 | LFX. | T1Sx | XCA | <b>A</b> Px | XT2OF | LFXT10F |  |  |

- **XT2Sx**: Seleção de intervalo XT2. Esses bits selecionam a faixa de frequência para XT2:

- 00 Cristal ou ressonador de 0,4 a 1 MHz;

- 01 Cristal ou ressonador de 1 a 3 MHz:

- ▶ 10 Cristal ou ressonador de 3 a 16 MHz:

- 11 Fonte externa de relógio digital de 0.4 a 16 MHz.

- LFXT1Sx: Seleção de clock de baixa frequência e seleção de faixa LFXT1. Esses bits selecionam entre LFXT1 e VLO quando XTS = 0 e selecione a faixa

de frequência para LFXT1 quando XTS = 1.

- Quando XTS = 0:

- 00 Cristal 32768-Hz em LFXT1:

- 01 Reservado:

- 10 VLOCLK (Reservado nos dispositivos MSP430F21x1);

- 11 Fonte de relógio externo digital.

- Quando XTS = 1 (Não aplicável para dispositivos MSP430x20xx, MSP430G2xx1 / 2/3):

- 00 Cristal ou ressonador de 0,4 a 1 MHz;

- 01 Cristal ou ressonador de 1 a 3 MHz:

- 10 Cristal ou ressonador de 3 a 16 MHz:

- 11 Fonte externa de relógio digital de 0.4 a 16 MHz.

- Definicão LEXT1Sx para dispositivos MSP430AFE2xx:

- 00 Reservado;

- 01 Reservado;

- 10 VLOCLK:

- 11 Reservado;

# Clock - BCSCTL3, Reg. de controle do clock do sistema 3

20 de iulho de 2018

8 / 15

| BCSCTL3       |                 |     |             |       |         |  |  |  |

|---------------|-----------------|-----|-------------|-------|---------|--|--|--|

| 7             | 7 6 5 4 3 2 1 0 |     |             |       |         |  |  |  |

| XT2Sx LFXT1Sx |                 | XCA | <b>A</b> Px | XT2OF | LFXT10F |  |  |  |

- XCAPx: Seleção de capacitores osciladores. Esses bits selecionam a capacitância efetiva vista pelo cristal LFXT1 quando XTS = 0. Se XTS = 1 ou se

- LFXT1Sx = 11 XCAPx deve ser 00:

- ▶ 00 ~ 1 pF;

- ▶ 01 ~ 6 pF;

- ▶ 10 ~ 10 pF;

- ▶ 11 ~ 12.5 pF.

- XT2OF: Falha do oscilador XT2:

- 0 Nenhuma condição de falha presente;

- 1 condição de falha presente.

- LFXT10F: Falha do oscilador LFXT1:

- 0 Nenhuma condição de falha presente;

- 1 condição de falha presente.

#### Clock - IE1, Reg. de ativação de interrupção 1

| IE1 |   |   |   |   |   |      |   |  |

|-----|---|---|---|---|---|------|---|--|

| 7   | 6 | 5 | 4 | 3 | 2 | 1    | 0 |  |

|     |   |   |   |   |   | OFIE |   |  |

- OFIE: Falha de interrupção de falha do oscilador. Este bit ativa a interrupção do OFIFG. Como outros bits no IE1 podem ser usados para outros módulos, é recomendável definir ou limpar esse bit usando as instruções BIS.B ou BIC.B, em vez das instruções MOV.B ou CLR.B.

- 0 interrupção não ativada;

- 1 interrupção ativada.

#### Clock - IFG1, Reg. da flag de interrupção 1

| IFG1  |   |   |   |   |   |   |   |  |

|-------|---|---|---|---|---|---|---|--|

| 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| OFIFG |   |   |   |   |   |   |   |  |

- **OFIFG**: Sinalizador de interrupção de falha do oscilador. Como outros bits no IFG1 podem ser usados para outros módulos, é recomendável definir ou limpar esse bit usando as instruções BIS.B ou BIC.B, em vez das instruções MOV.B ou CLR.B.

- Nenhuma interrupção pendente;

- 1 Interrupção pendente.

#### Clock - Exemplo de conf. da fonte clock por VLOCLK

```

\#include < msp430.h >

// Segundo a Texas, essas linhas sao para ajustar uma pequena inconssistencia

// que pode ocorrer entre os microcontroladores g2553 e g2231

#ifndef TIMERO A1 VECTOR

#define TIMERO A1 VECTOR TIMERA1 VECTOR

#define TIMERO AO VECTOR TIMERAO VECTOR

#endif

int main(void)

WDTCTL = WDTPW | WDTHOLD:

// O watchdog timer permanece parado

P1DIR = BIT6:

P1OUT = 0 \times 00:

BCSCTL3 |= LFXT1S 2:

//LFXT1S 2 = VLOCLK

IFG1 &= ~OFIFG:

//OFIFG = falha do oscilador

_bis_SR_register(SCG1+SCG0);

BCSCTL2 |= SELM_3 + DIVM_3;

//SELM 3 = VLOCLK: DIVM 3 = MCLK/8

while (1) {

P10UT = BIT6:

_delay_cycles(1000);

P1OUT = 0:

delay cycles (1000):

```

#### Clock - Exemplo de conf. da fonte clock por LFXT1CLK

```

#include <msp430.h>

#ifndef TIMERO A1 VECTOR // Segundo a Texas, essas linhas sao para ajustar uma pequena inconssistencia

#define TIMERO_A1_VECTOR TIMERA1_VECTOR // que pode ocorrer entre os microcontroladores g2553 e g2231

#define TIMERO AO VECTOR TIMERAO VECTOR

#endif

int main(void)

WDTCTL = WDTPW | WDTHOLD; // O watchdog timer permanece parado

P1DIR = 0 \times 41:

P1OUT = 0 \times 01:

BCSCTL3 |= LFXT1S 0 + XCAP 3: //LFXT1S 0 = Cristal em LFXT1: XCAP 3 = Capacitor do oscilador em 12.5 pF

while (IFG1 &= OFIFG) {

IFG1 &= ~OFIFG:

delay cycles(100000):

P1OUT = 0:

bis SR register(SCG1+SCG0):

BCSCTL2 = SELM 3 + DIVM 3: //SELM 3 = LFXT1CLK: DIVM 3 = MCLK/8

while (1) {

P1OUT = BIT6:

_delay_cycles(1000);

P1OUT = 0;

_delay_cycles(1000);

```

#### Clock - Exemplo de conf. da fonte clock por DCOCLK

```

#include <msp430.h>

#ifndef TIMERO A1 VECTOR // Segundo a Texas, essas linhas sao para ajustar uma pequena inconssistencia

#define TIMERO_A1_VECTOR TIMERA1_VECTOR // que pode ocorrer entre os microcontroladores g2553 e g2231

#define TIMERO AO VECTOR TIMERAO VECTOR

#endif

int main(void)

WDTCTL = WDTPW | WDTHOLD; // O watchdog timer permanece parado

P1DIR = 0 \times 41:

P1OUT = 0 \times 01:

if ((CALBC1 1MHZ == 0 \times FF) || (CALDCO 1MHZ == 0 \times FF)){

while (1):

BCSCTL1 = CALBC1 1MHZ; //CALBC1_1MHZ = Calibra o DCO no BCSCTL1 para 1MHz

DCOCTL = CALDCO 1MHZ: //CALDCO 1MHZ = Calibra o DCO no DCOCTL para 1MHz

BCSCTL3 |= LFXT1S_0 + XCAP_3; //LFXT1S_0 = Cristal em LFXT1; XCAP_3 = Capacitor do oscilador para 12.5 pF

while (IFG1 &= OFIFG) {

IFG1 &= ~OFIFG:

delay cycles(100000):

BCSCTL2 = SELM 0 + DIVM 3: //SELM 0 = DCOCLK: DIVM 3 = MCLK/8

while (1) {

P1OUT = BIT6:

_delay_cycles(1000);

P1OUT = 0;

delay cycles(1000):

```

#### Referências

- MSP403×2×× Family, User's Guide, revised July 1013;

- Getting Started with the MSP430 LaunchPad, Student Guide and Lab Manual, revision 2.01 February 2012.

# Seja 100 % Motivado!